Intel exhibió una gran tecnología en Hot Chips 2023, más allá de los chips de servidor. Tenía una textura visual sencilla de cuadrícula en cuadrícula. Lo que también podría ser interesante es el procesador octa core que tiene 66 subprocesos por núcleo.

Nuevamente, disculpe los errores tipográficos, esto se hará en vivo.

Intel presenta el primer tejido óptico directo de red a red del mundo

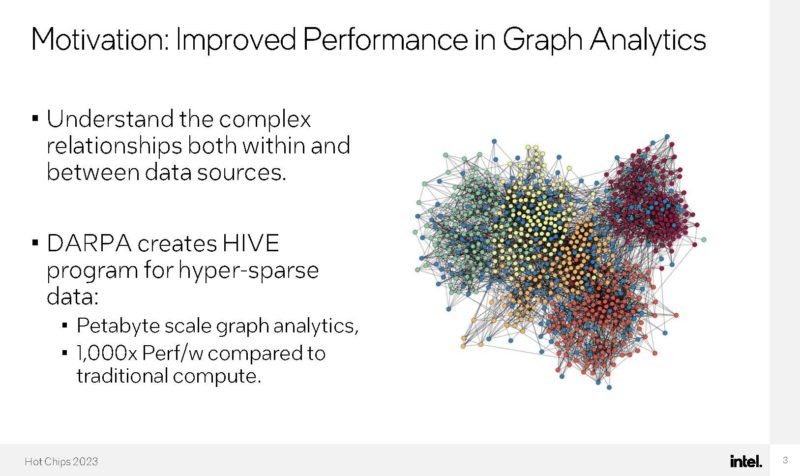

Esto fue impulsado principalmente por el programa de datos altamente disperso DARPA HIVE.

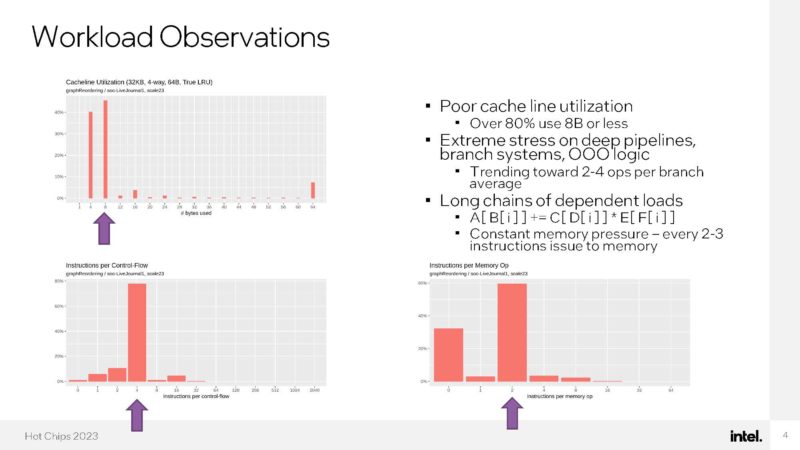

Cuando Intel definió las cargas de trabajo que DARPA estaba analizando, descubrió que eran en gran medida paralelas. Sin embargo, tenían un uso deficiente de la caché de línea y cosas como canalizaciones grandes, largas e inválidas no se aprovecharon.

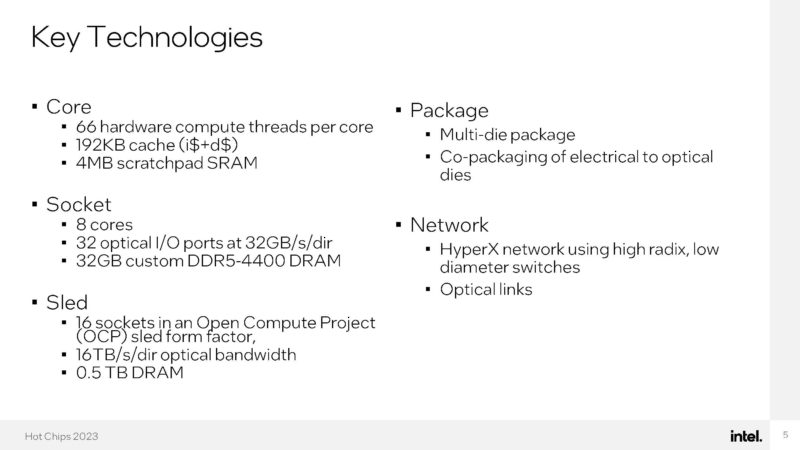

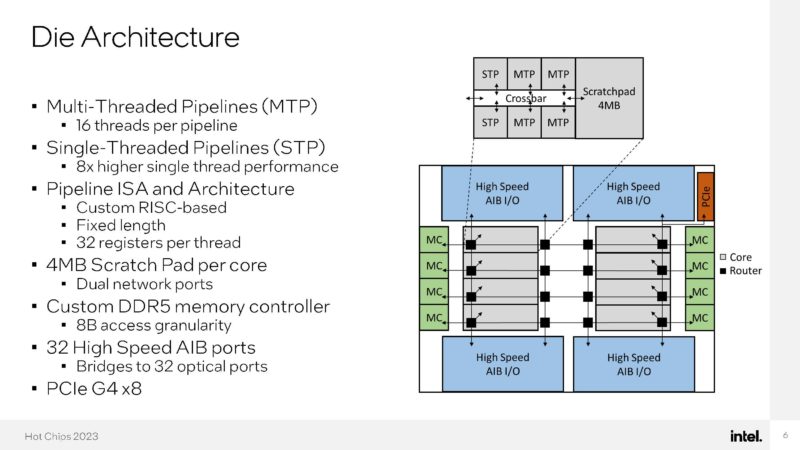

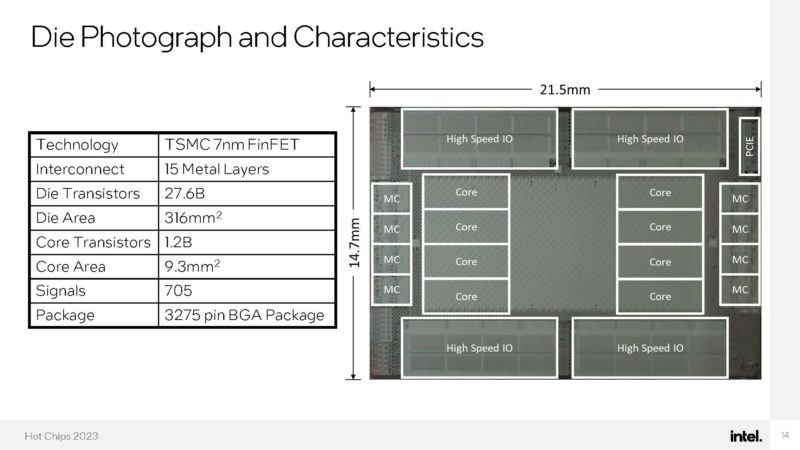

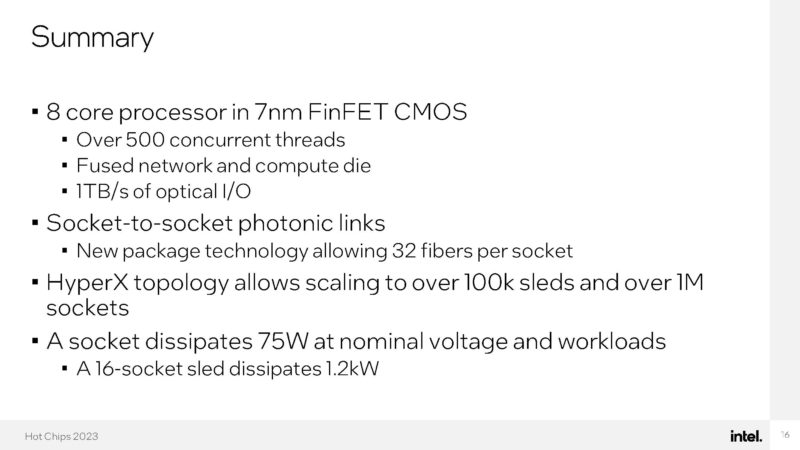

Aquí hay uno interesante. Intel tiene un procesador con 66 hilos por núcleo con 8 núcleos en el socket (¿528 hilos?) y el caché parece estar infrautilizado debido a la carga de trabajo. Este es RISC ISA, no x86.

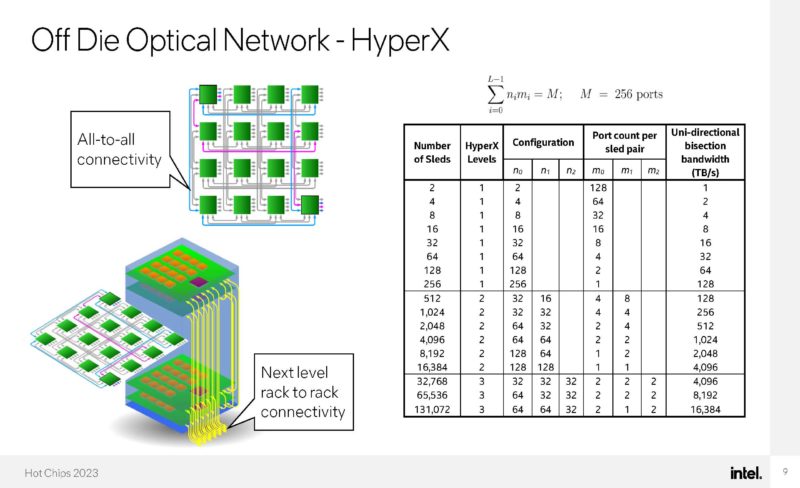

Intel los agrupa en 16 zócalos en un único hilo de cálculo para OCP y el uso de redes ópticas.

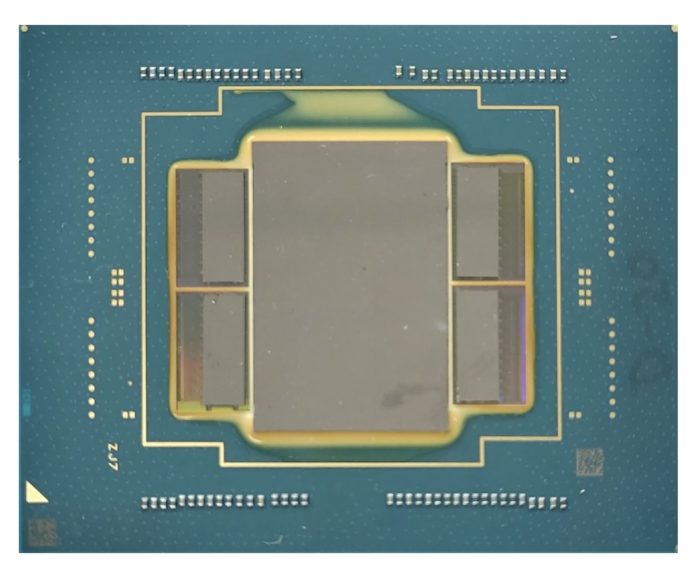

Aquí está la arquitectura morir. Cada núcleo contiene canalizaciones de subprocesos múltiples.

El chipset de E/S de alta velocidad combina las capacidades eléctricas y ópticas del chip.

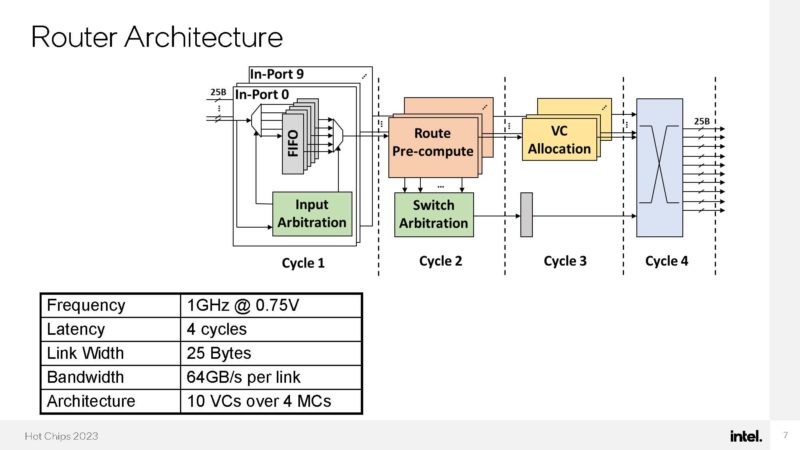

Aquí se utiliza el enrutador de 10 puertos.

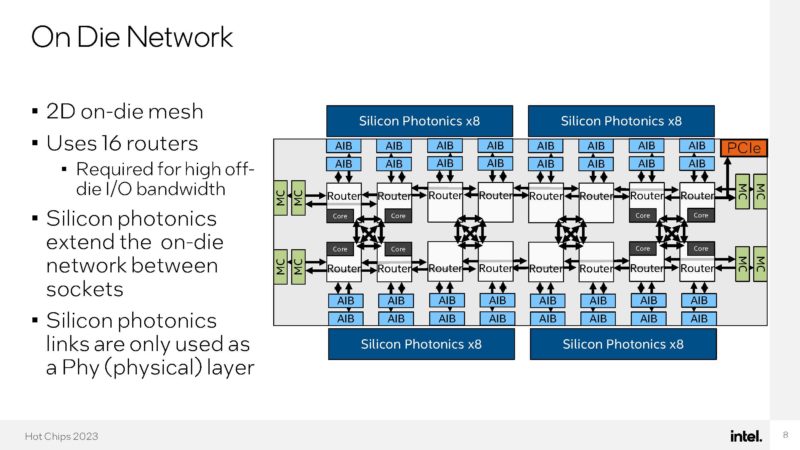

Esta es la red existente donde se colocan los enrutadores. La mitad de los 16 enrutadores están ahí sólo para proporcionar más ancho de banda para E/S de alta velocidad. Los EMIB empaquetados se utilizan para la capa de comunicación física.

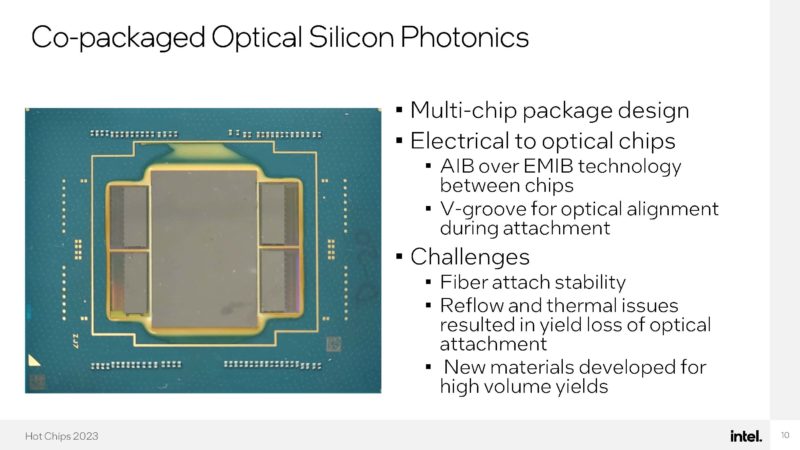

Al salir del molde, cada chip utiliza fotónica de silicio para alimentar su red fotónica. Con esto, las comunicaciones entre núcleos se pueden realizar directamente entre chipsets aunque no estén en el mismo chasis sin necesidad de añadir adaptadores y NIC.

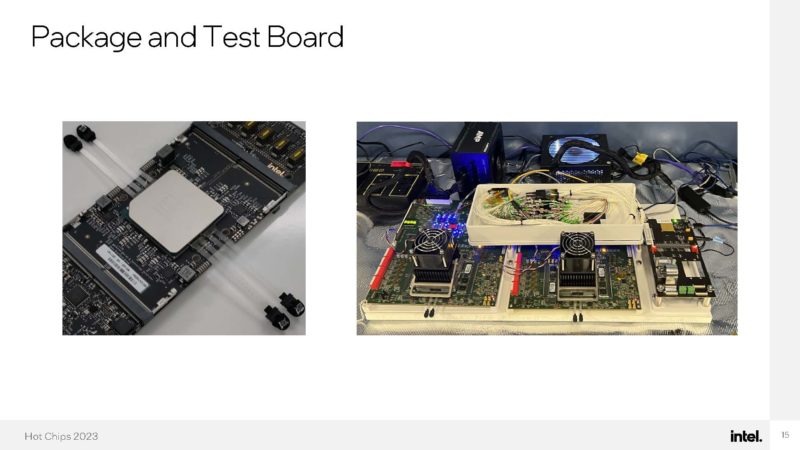

Estos chips están empaquetados como un paquete de múltiples chips con EMIB. La presencia de la fotónica de silicio ha añadido algunos desafíos más al pasar del embalaje a los filamentos de fibra.

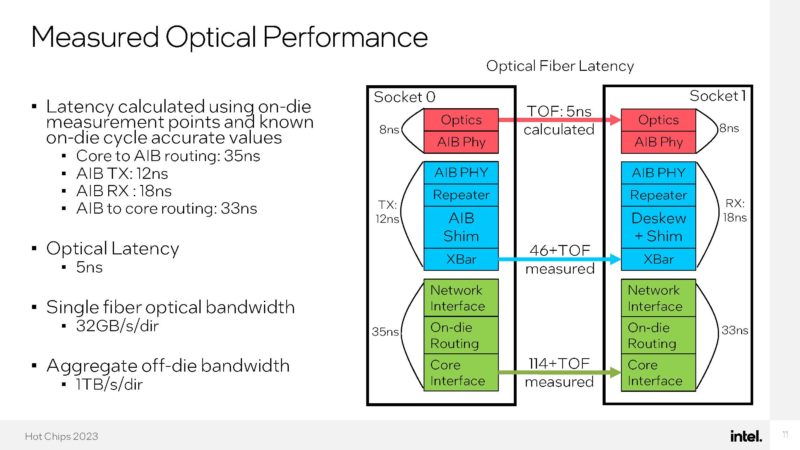

Aquí está el rendimiento visual.

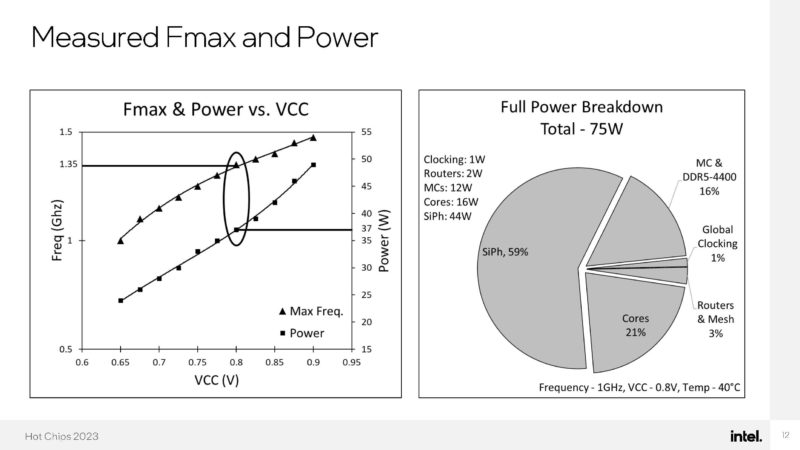

En términos de potencia, esto se hizo en una CPU de 8 núcleos con 75 vatios. Más de la mitad de la energía aquí es utilizada por la fotónica de silicio.

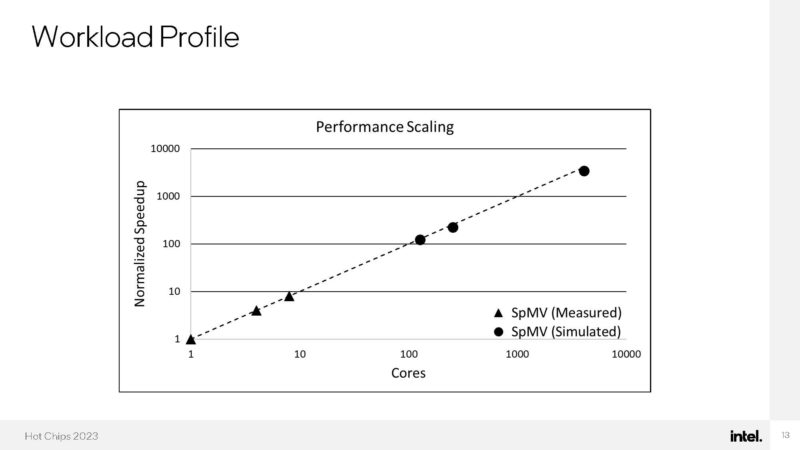

A continuación se muestra una simulación de la medición del rendimiento de la carga de trabajo.

Aquí está la imagen real y la confirmación de que esto se está haciendo en TSMC de 7 nm.

Así es como se ven el paquete y el tablero de prueba:

Esto se hizo con tecnología de 7 nm y todavía se está trabajando en ello en el laboratorio.

ultimas palabras

Fue interesante ver que Intel no usó el conector enchufable que mostró en Innovation 2022. Parece que esto pudo haber sido diseñado antes de que este proyecto estuviera listo. Aiyer Labs ayudó en esto en el aspecto visual.

¡Quizás el más importante sea el de 66 subprocesos por núcleo! Este es un número enorme. Creo que la gente disfrutará este proyecto de ley.

«Organizador. Escritor. Nerd malvado del café. Evangelista general de la comida. Fanático de la cerveza de toda la vida.